I, Elena CERBARO, an Italian citizen, residing at 10125 TORINO, Corso Raffaello No. 15 (Italy), being acquainted with the Italian and English languages, certify that the attached is an accurate translation into the English language of the certified copy relating to European Patent Application No. 02 425 016.7 filed on January 15, 2003.

Iluer Culms

Dated this 29th day of July, 2005

THE PACK OF MANY MONTO

10

15

30

SUBLITHOGRAPHIC CONTACT STRUCTURE, IN PARTICULAR FOR A PHASE CHANGE MEMORY CELL, AND FABRICATION PROCESS THEREOF

The present invention relates to a sub lithographic contact structure, in particular for a phase change memory cell, and a fabrication process thereof.

As is known, phase change memory cells utilize a class of materials that have the unique property of being reversibly switchable from one phase to another with measurable distinct electrical properties associated with each phase. For example, materials may change between an amorphous disordered phase and a crystalline, or polycrystalline, ordered phase. A material property that may change and provide a signature for each phase is the material resistivity, which is considerably different in the two states.

At present, alloys of elements of group VI of the periodic table, such as Te or Se, referred to as chalcogenides or chalcogenic materials, can advantageously be used in phase change cells. The currently most promising chalcogenide is formed by a Ge, Sb and Te alloy (Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>), which is currently widely used for storing information in overwritable disks.

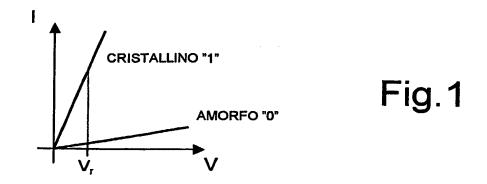

In chalcogenides, the resistivity varies by two or more magnitude orders when the material passes from the amorphous phase (more resistive) to the polycrystalline phase (more conductive) and vice versa, as shown in Figure 1. Furthermore, in the amorphous phase, resistivity strongly depends also on temperature, with variations of one magnitude order every 100°C, with a behavior similar to that of P-type semiconductor

THIS PROPERTY USPRO

materials.

10

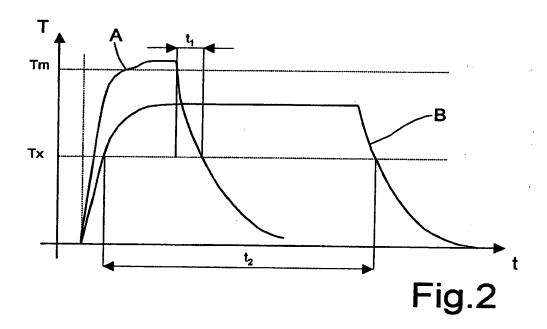

Phase change may be obtained by locally increasing the temperature, as shown in Figure 2. Below 150°C both phases are stable. Above 200°C (temperature of start of nucleation, designated by  $T_x$ ), fast nucleation of the crystallites takes place, and, if the material is kept at the crystallization temperature for a sufficient (time  $t_2$ ), it changes its phase and becomes crystalline. To bring the chalcogenide back into the amorphous state, it is necessary to raise temperature above the melting temperature (approximately 600°C) and then to cool the chalcogenide off rapidly (time  $t_1$ ).

From the electrical standpoint, it is possible to reach both critical temperatures, namely the crystallization and the melting temperatures, by causing a current to flow through a resistive element which heats the chalcogenic material by the Joule effect.

The basic structure of a PCM element 1 which operates according to the principles described above is shown in Figure 3 and comprises a first electrode 2 (of resistive type, forming a heater); a programmable element 3 and a second electrode 5. The programmable element 3 is made of a chalcogenide and is normally in the polycrystalline state after processing. One part of the programmable element 3 is in direct contact with the first electrode 2 and forms the active portion affected by phase change, hereinafter referred to as the phase change portion 4.

In the PCM element 1 of figure 3, technological and electrical considerations impose that the contact area between the first electrode and the programmable element has small dimensions, so that, for the same

THIS PROCEDURANT USPO,

current density, the writing operation may be carried out at the required local thermal energy with smaller current consumption.

Several proposals have been presented for reducing the contact area. For example, US-A-6,294,452 discloses a process for forming a contact area of sublithographic dimensions, based on isotropically etching a polysilicon layer. The resulting sublithographic dimensions depend on the quality of the etching.

US 2001/0002046 discloses a process for forming an electrode of a chalcogenide switching device, wherein a spacer layer deposited in a lithographic opening is anisotropically etched and laterally defines an electrode. The resulting width of the electrode depends on the thickness of a spacer layer.

European patent application 01128461.9, filed on 5.12.2001, and entitled "Small area contact region, high efficiency phase change memory cell, and manufacturing method thereof", teaches forming the contact area as an intersection of two thin portions extending transversely with respect to one another and each of a sublithographic size. In order to form the thin portions, deposition of layers is adopted.

20

25

30

In all the indicated prior solutions, any variation in the electrode width L (Figure 3), due for example to the process tolerances, affects, in a linear way, the contact area of the active region 4. Thus, the width L may have tolerances that are not acceptable as regards repeatability and uniformity of the cell characteristics.

The object of the invention is thus to provide a contact region having an area less dependent on the process variations.

According to the present invention, there are

THIS PAGE BURNEY USONO,

provided an electronic semiconductor device and a process for manufacturing an electronic semiconductor device, as defined respectively in claims 1, and 9.

According to one aspect of the invention, the contact area is formed laterally to the active region and has a height and width. Advantageously, the height of the contact area is determined by the thickness of a deposited layer, which is technologically controlled and may be designed to be sublithographic. Furthermore, according to another aspect of the invention, the width of the contact area is determined by the width of a spacer which may also be designed of sublithographic dimensions and may be dimensionally controlled with a good accuracy.

10

20

30

For the understanding of the present invention, a preferred embodiment is now described, purely as a non-limitative example, with reference to the enclosed drawings, wherein:

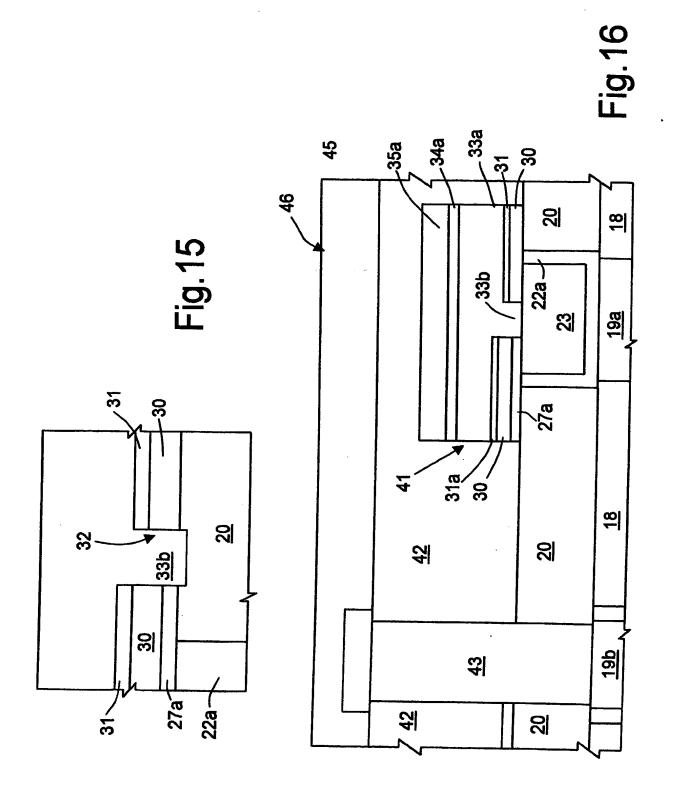

- Figure 1 illustrates the characteristic low field current-voltage of a phase change material;

- Figure 2 shows the temperature versus time plot of a phase change material;

- Figure 3 shows the basic structure of a PCM memory element;

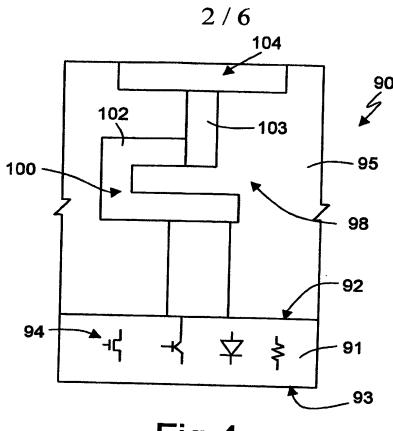

- 25 Figure 4 shows a cross-section of a contact structure according to the present invention;

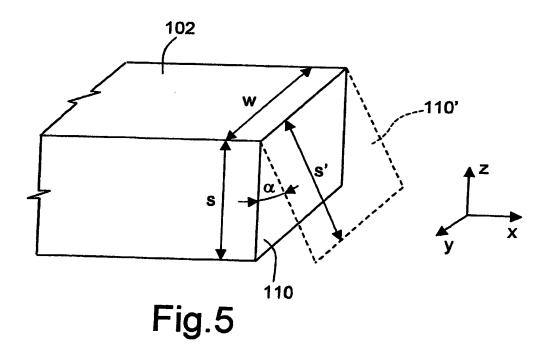

- Figure 5 is a perspective view of a portion of the contact structure of Figure 4 showing the variability of the contact area due to technological tolerances;

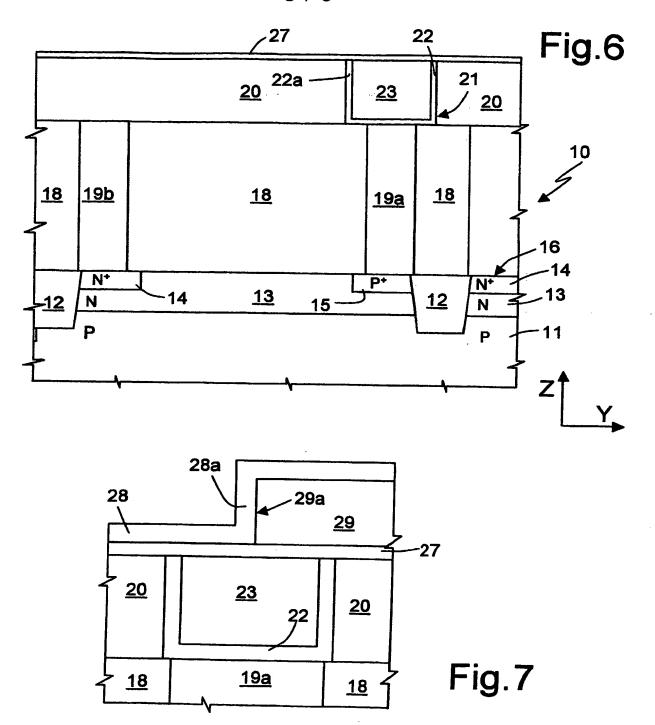

- Figure 6 is a cross-section of a PCM memory element in an initial manufacturing step;

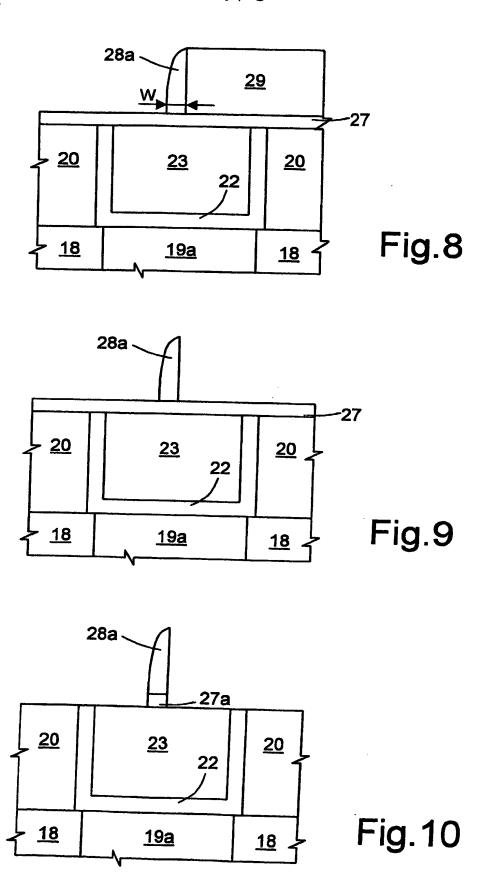

- Figures 7-11 are cross-sections of an enlarged detail of Figure 6, in subsequent manufacturing steps;

THIS PACK BLANK ASOTO,

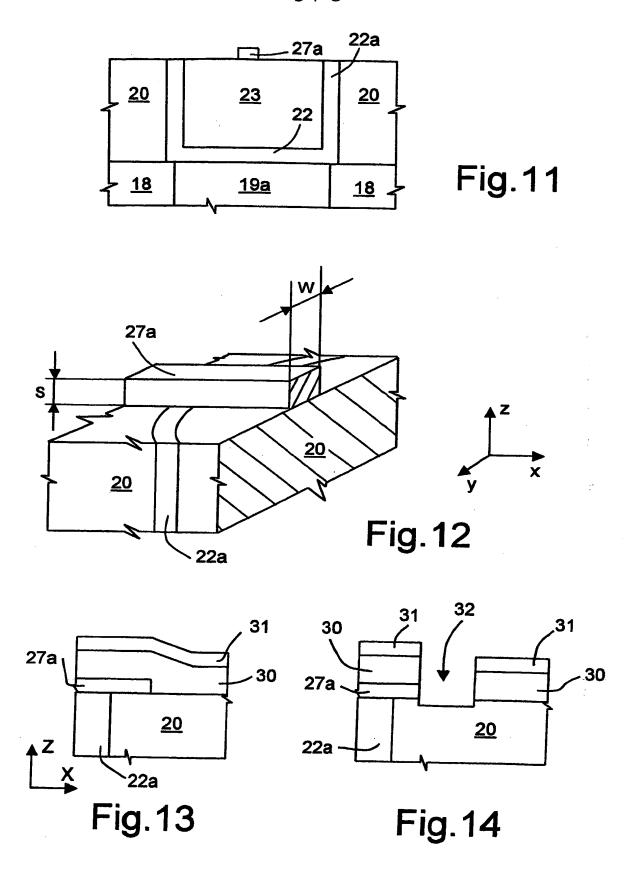

- Figure 12 is a perspective view of the structure of Figure 11; and

- Figures 13-16 are cross-sections of the PCM memory element, in subsequent manufacturing steps, taken in a perpendicular plane with respect to Figures 7-11.

Figure 4 illustrates the basic structure of a structure according to the invention. detail, an electronic device 90 has a body 91 (e.g. a 10 of monocrystalline material substrate) defining an surface 92 and a lower surface 93 upper accommodating electronic components 94, represented schematically. A dielectric layer 95 extends on top of the body 91 and accommodates the contact structure, 15 indicated at 98. The contact structure 98 is formed by a first electrode 100 and an active region 103 of chalcogenic material. The first electrode connected to the electronic components 94 as shown schematically for one of them, has a horizontal portion 20 102 adjacent to and in contact with the active region 103. A second electrode 104 is formed on the active region 103 and is in electric contact therewith.

As better shown in the perspective view Figure 5, the horizontal portion 102 has an elongated shape extending along a longitudinal direction X parallel to the upper and lower surfaces 92, 93 of the body 91. The horizontal portion 102 is longitudinally delimited by an end face 110. The end face 110 extends in a vertical plane, which is ideally perpendicular longitudinal direction X and thus to the upper and lower surfaces 92, 94 and defines a lateral contact area with the active region 103. The end face 110 is here rectangular and has a height S (extending parallel to direction Z) and a width W (extending parallel to

25

30

THIS PORT OF THE PROPERTY.

direction Y). The portion of the active region 103 adjacent to the end face 110 undergoes phase change and thus corresponds to the active region 4 of Figure 3.

Because of the vertical arrangement of the end face 110 and thus of the contact area, the height S is equal to the thickness of the horizontal portion 102 of the first electrode 100, and thus may be designed to be sublithographic, that is smaller than the minimum dimension obtainable through optical UV lithography.

In practice, the contact structure 98 according to Figures 4, 5 is formed by an elongated formation (horizontal portion 102 of the first electrode 100) having a longitudinal extension parallel to the upper surface 92 of the body 91 and an end face 110 extending in a vertical plane and in contact with the active region 103 so that the dimensions of the contact area (defined by the end face 110) are determined by the thickness S of the elongated formation and by the width W thereof.

20

25

The height S of the horizontal portion 102 and thus of the contact area is more controllable than the electrode width L of prior art contact structures so that PCM cells having the contact (Figure 3), structure of Figure 4 have more uniform dimensions than The thickness tolerance cells. prior art conductive layer forming the horizontal portion 102 overall dimensions, allows. for same а higher constructive confidence than electrodes the contact area whereof depends on the width L.

The height S also depends on the quality of the operation used to define the end face 110, in particular by the etching operation used to this end. Figure 5 shows the possible variation of the contact area in case etching does not ensure exact verticality

THIS PROCE BLANK USERO,

of the end face 110, so that horizontal portion 102 has an inclined end face, indicated at 110', forming an angle  $\alpha$  with ideal end face 110 (which, as said, is perpendicular to the upper surface 92). In this case, the height S' of the inclined end face 110' is greater than height S by a quantity depending on the angle  $\alpha$ , since

$S' = S/\cos\alpha$ .

25

30

In the worst cases, with current technologies,  $\alpha \le 5^{\circ}$ , so that  $\cos\alpha \cong 1$  [ $\cos(5^{\circ})=0.99619$ ]. Since any variation of height S has the same impact on the contact area, the variation of the contact area due to process tolerances affecting the height S is lower than  $2^{\circ}$ .

Furthermore, also the width W may be sublithographic, by exploiting the spacer technique, as discussed later on, with reference to Figures 7-12. This technique has a tolerance of  $\pm 10\%$ .

The process for manufacturing the contact structure of Figure 4 will be now described, with reference to Figures 6-16.

First, Figure 6, a wafer 10 comprising a P-type substrate 11 having an upper surface 16 is subjected to standard front end steps. In particular, inside the substrate 11 insulation regions 12 are formed and delimit active areas; then, in succession, base regions 13 of N-type, base contact regions 14 of N $^+$ -type, and emitter regions 15 of P $^+$ -type are implanted. The base regions 13, base contact regions 14, and emitter regions 15 form diodes or bipolar transistors that define selection elements for the memory cells.

Next, a first dielectric layer 18 is deposited and planarized; openings are formed in the first dielectric layer 18 above the base contact regions 14 and emitter

THIS PAGE BLANK USDO)

regions 15, and the openings are filled with tungsten to form emitter contacts 19a and base contacts 19b. Then, a second dielectric layer 20 -for example, an undoped silicon glass (USG) - is deposited, and openings 21, for example, cylindrical-shaped, are formed in the second dielectric layer 20 above the emitter contact 19a. Next, a cup-shaped region 22 is formed, e.g. by depositing an electrode layer, for example of TiSiN, TiAlN or TiSiC, that conformally coats the walls and bottom of the openings 21, a dielectric material is then deposited filling the openings 21, and then the dielectric material and electrode layer are subsequently removed outside the openings 21, using conventional planarization techniques such as Chemical Mechanical Polishing (CMP). The cup-shaped region 22 thus has a vertical wall 22a extending along the cylindrical side surface of the openings 21.

10

15

20

30

Then, a conductive layer 27 (for instance TaSiN, TiSiN, TiN, TiAlN, etc.) having a thickness of 5-50 nm, corresponding to the desired height S of the contact area 110 is deposited, thus obtaining the structure of Figure 6. As visible, the conductive layer 27 extends parallel to the upper surface 16 of substrate 11.

At this point, a mask is exposed and the conductive 25 layer 27 is selectively etched in order to form stripes parallel to the y-direction.

The width of these stripes has to be enough to ensure that the strips touch the conductive ring formed by the vertical walls 22a on one side and be cut by the trench etch described in Fig.14 on the other side.

Next, Figure 7, a delimiting layer 29 of insulating material, for example oxide, is deposited. The delimiting layer 29 has a thickness of, for instance, 20-200 nm. Then, using a mask, one part of the

THIS PAGE BLANK USPTO,

delimiting layer 29 is removed by dry etching to form a step which has a vertical side 29a that extends vertically on top of the dielectric material 23, and crosses the vertical wall 22a of cup-shaped region 22 (at a point located before or behind the drawing plane, and thus not visible in Figure 7).

5

10

20

25

Next, a sacrificial layer 28, for example nitride with a thickness of 5-50 nm, is deposited conformally. In particular, the sacrificial layer 28 forms a vertical wall 28a that extends along the vertical side 29a of the delimiting layer 29. Thus, the structure of Figure 7 is obtained.

Thereafter (Figure 8), the sacrificial layer 31 undergoes an anisotropic etching that results in removal of the horizontal portions of the sacrificial layer 28 and of part of the vertical wall 28a. By appropriately choosing the thickness of the delimiting layer 29 and the thickness of the sacrificial layer 28, as well as the time and type of etching, it is possible to obtain the desired sublithographic width W for the bottom part of the remaining vertical wall 28a.

Then, Figure 9, the remaining portion of the delimiting layer 29 is removed and, Figure 10, using the vertical wall 28a as a hard mask, the conductive layer 27 is defined. Thereafter, Figure 11, the vertical wall 28a is removed.

Now, as shown in perspective in Figure 12, the remaining portion of the conductive layer 27 (stripshaped portion 27a) has a height S and a width W.

30 Thereafter, Figure 13, an insulating layer 30 (e.g. silicon oxide) and an adhesion layer 31 (e.g. Si, Ti, Ta, etc.) are deposited in sequence.

Then, Figure 14, a trench 32 of lithographic dimensions is opened. The trench 32 is an aperture

THIS PACE BLANK USOTO,

having a preset length in the direction perpendicular to the drawing sheet, intersects the strip-shaped portion 27a and extends within the second dielectric layer 20 so as to longitudinally delimit the strip-shaped portion 27a. In practice, the trench 32 determines the length L1 of the strip-shaped portion 27a.

Thereafter, Figure 15, a chalcogenic layer 33, for example of  $Ge_2Sb_2Te_5$  having a thickness of e.g. 20-200 nm, is conformally deposited and fills the trench 32 with a reduced area portion 33b the shape and dimensions whereof are determined by the trench 32.

10

Then, a barrier layer 34, for example of Ti/TiN, and a metal layer 35, for example of AlCu, 15 deposited in sequence on top of the chalcogenic layer 33; the stack formed by the metal layer 35, the barrier layer 34 and the chalcogenic layer 33 is defined using a same mask, thus forming a bit line 41 including a chalcogenic region 33a and metal regions 34a, 20 Finally, a third dielectric layer 42 is deposited, which is opened above the base contacts 19b. openings thus formed are filled with tungsten to form top contacts 43 in order to prolong upwards the base contacts 19b. Then standard steps are performed for 25 forming connection lines in contact with the top contacts 43 and with the bits lines 41, pads are formed and a passivation layer 45 is deposited, defining a device main surface 46. Thus, the final structure of Figure 16 is obtained.

In practice, the strip-shaped portion 27a (corresponding to the horizontal portion 102 of the first electrode 100 of Figure 4) has a longitudinal extension parallel to upper surface 16 of the substrate 11 and forms, with the bottom portion of the reduced

THIS PAGE BLANK USPO,

area portion 33b, a contact area the height whereof is defined by the thickness of the conductive layer 27 and the width whereof is defined by the thickness of the sacrificial layer 28. The quality of the etching of trench 32 determines the orientation of the contact area with respect to the upper surface 16.

The advantages of the present invention are clear from the above. In particular, it is outlined that the present contact structure has a very good technological repeatability, a lower dependence from the process variations than prior art solutions, while maintaining a very small contact area, having sublithographic dimensions in both directions.

10

20

25

Finally, it is clear that numerous variations and modifications may be made to the contact structure and process described and illustrated herein, all falling within the scope of the invention as defined in the attached claims.

In particular, it is stressed that the direction of the horizontal portion 102 and the conductive layer 27 is defined with reference to the upper surface 92, 16 substrate, intending therewith plane corresponding to the original upper surface of the wafer. In practice, the horizontal portion 102 and the conductive layer 27 are perpendicular to the direction of growing of the substrate, due to the deposition of the various superficial layers. If, due to deposition, thermal growing, etching and implant steps carried out on the wafer, the upper surface 16 of the finished device is no more planar, reference may be done to the lower surface 93 of the substrate or to the device main surface 46.

Moreover an alternative embodiment of the present invention provides that the conductive layer 27 is in

THIS PAGE BLANK USPTO,

direct contact with the emitter layer 19a, thus avoiding the dielectric layers 20 and 23 and the cupshaped region 22.

THIS PAGE BLANK USPTO)

## CLAIMS

- 1. An electronic semiconductor device (90), comprising:

- a body (91; 11) of semiconductor material having an 5 upper surface (92; 16);

- a dielectric layer (95; 20, 42) extending on top of said body;

- a contact structure (98) in said dielectric layer, said contact structure comprising a first conducting 10 region (102; 27a) and a second conducting region (103; 33a), said second conducting region being of chalcogenic material and being in electric contact with said first conducting region;

- characterized in that said first conducting region (102; 27a) has a strip-like shape having a longitudinal direction delimited by an end face (110) extending transversely to said upper surface (92; 16) and forming a contact area with said second conducting region (103; 33a).

- 2. A device according to claim 1, wherein said first conducting region (102; 27a) extends in a first direction (X) parallel to said upper surface (92; 16).

25

- 3. A device according to claim 1 or 2, wherein said end face (110) is perpendicular to said upper surface (92; 16) within process tolerances.

- 4. A device according to any of claims 1-3, wherein said end face (110) has a generally rectangular shape having a height (S) and a width (W).

- 5. A device according to claim 4, wherein said 30 height (S) is comprised between 5 nm and 50 nm and said width (W) is comprised between 5 nm and 50 nm.

- 6. A device according to any of claims 1-4, forming a PCM device including a memory cell comprising a

THIS PAGE BLANK USPTO,

selection element (13-15) and a storage element, said storage element being formed by a heater element (22a, 27a) including said first conducting region (27a) and a storage region (33a) comprising said second conducting region.

5

10

- 7. A device according to claim 6, wherein said selection element (13-15) is formed in said body (11), a lower electrode (19a) extends in said dielectric layer (20, 42) between said selection element and said first conducting region (27a) and an upper electrode (35a) extends in said dielectric layer on said second conducting region (33a) and forms a bit line.

- 8. A device according to claim 7, wherein said second conducting region (33a) has a reduced area portion (33b) in contact with said first conducting region (27a) and an upper enlarged portion extending on top of said reduced area portion and in contact with said upper electrode (35a).

- 9. A process for manufacturing an electronic 20 semiconductor device (90), comprising the steps of:

providing a body (91; 11) of semiconductor material having an upper surface (92; 16);

forming a dielectric layer (95; 20, 42) extending on top of said body; and

forming a contact structure (98) in said dielectric layer, said step of forming a contact structure comprising forming a first conducting region (102; 27a) and forming a second conducting region (103; 33a) of chalcogenic material in electric contact with said first conducting region;

characterized in that said step of forming said first conducting region comprises forming a strip-shaped region (102; 27a) having a longitudinal

THIS PAGE BLANK USPRO,

direction delimited by an end face (110) extending transversely to said upper surface (92; 16);

and said step of forming a second conducting region comprises forming said second conducting region (103; 33a) in contact with said first conducting region at said end face.

5

10

20

25

- 10. A process according to claim 9, wherein said end face (110) has a generally rectangular shape having a height (S) comprised between 5 nm and 50 nm and a width (W) comprised between 5 nm and 50 nm.

- 11. A process according to claim 9 or 10, wherein said step of forming said first conducting region (27a) comprises depositing a first conductive layer (27) on a bottom portion (20) of said dielectric layer (20, 42); 15 forming a delimitation layer (29) on top of said first conductive layer, said delimitation layer (29) having a step with a vertical side wall surface (29a); forming a sacrificial portion (28a) on said vertical side wall surface; removing said first delimitation layer (29); etching said first conductive layer (27a) using said a sacrificial portion (28a) as a mask; and removing said sacrificial portion.

- 12. A process according to claim 11, wherein said step of forming a sacrificial portion (28a) comprises depositing a sacrificial layer on said first conducting region and said delimitation layer (29)anisotropically etching said sacrificial layer (28).

- 13. A process according to claim 11 or 12, wherein after removing said sacrificial portion (28a), insulating layer (30) is deposited on said first 30 conducting region (27a) and said bottom portion of said dielectric layer (20, 42); a trench (32) is formed to remove at least a portion of said bottom portion and an

THIS PACE BLANK USPTO,

end portion of said first conducting region, thereby defining said end face (110); and a second conductive layer (33) of said chalcogenic material is deposited, filling said trench (32) and contacting said end face (110).

5

10

- 14. A process according to claim 13, comprising the step of forming a PCM device including a memory cell comprising a selection element (13-15) and a storage element (33b), said storage element being formed by a heater element including said first conducting region and a storage region comprising said second conducting region.

- 15. A process according to claim 14, comprising, after depositing said second conductive layer (33), depositing an electrode layer (35) and defining said electrode layer and said second conductive layer, to define a bit line (41).

THIS PAGE BLANK USPTO)

## ABSTRACT

A contact structure (98) for a PCM device is formed by an elongated formation (102) having a longitudinal extension parallel to the upper surface (92) of the body (91) and an end face (110) extending in a vertical plane. The end face (110) is in contact with a bottom portion of an active region (103) of chalcogenic material so that the dimensions of the contact area defined by the end face (110) are determined by the thickness (S) of the elongated formation and by the width (W) thereof.

Figure 4

10

THIS PAGE BLANK USPRO,

Europäisches **Patentamt**

European **Patent Office**

Office européen des brevets

Bescheinigung

Certificate

Attestation

Die angehefteten Unterlagen stimmen mit der ursprünglich eingereichten Fassung der auf dem nächsten Blatt bezeichneten europäischen Patentanmeldung überein.

The attached documents are exact copies of the European patent application conformes à la version described on the following page, as originally filed.

Les documents fixés à cette attestation sont initialement déposée de la demande de brevet européen spécifiée à la page suivante.

Patentanmeldung Nr.

Patent application No. Demande de brevet n°

03425016.7

Der Präsident des Europäischen Patentamts; Im Auftrag

For the President of the European Patent Office

Le Président de l'Office européen des brevets p.o.

R C van Dijk

THIS PAGE BLANK (USPTO)

European

Patent Office

Office européen des brevets

Anmeldung Nr:

Application no.: 03425016.7

Demande no:

Anmeldetag:

15.01.03

Date of filing: Date de dépôt:

Anmelder/Applicant(s)/Demandeur(s):

STMicroelectronics S.r.1. Via C. Olivetti, 2 20041 Agrate Brianza (Milano) ITALIE

Bezeichnung der Erfindung/Title of the invention/Titre de l'invention: (Falls die Bezeichnung der Erfindung nicht angegeben ist, siehe Beschreibung. If no title is shown please refer to the description. Si aucun titre n'est indiqué se referer à la description.)

Sublithographic contact structure, in particular for a phase change memory cell, and fabrication process thereof

In Anspruch genommene Prioriät(en) / Priority(ies) claimed /Priorité(s) revendiquée(s)

Staat/Tag/Aktenzeichen/State/Date/File no./Pays/Date/Numéro de dépôt:

Internationale Patentklassifikation/International Patent Classification/Classification internationale des brevets:

G11C13/00

Am Anmeldetag benannte Vertragstaaten/Contracting states designated at date of. filing/Etats contractants désignées lors du dépôt:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IT LU MC NL PT SE SI SK TR LI

THIS PAGE BLANK (USPTO)

STRUTTURA DI CONTATTO SUBLITOGRAFICA, IN PARTICOLARE

PER UNA CELLA DI MEMORIA A CAMBIAMENTO DI FASE, E

RELATIVO PROCEDIMENTO DI FABBRICAZIONE

La presente invenzione riguarda una struttura di contatto sublitografica, in particolare per una cella di memoria a cambiamento di fase, e il relativo procedimento di fabbricazione.

Come è noto, le celle di memoria a cambiamento di 10 fase utilizzano una classe di materiali che hanno la proprietà singolare di essere commutabili in modo reversibile tra una prima ed una seconda fase aventi resistenza distinta misurabile. Ad esempio, materiali possono cambiare fra una fase 15 disordinata, ed una fase cristallina o policristallina, ordinata. Una proprietà del materiale che può cambiare fornire un'indicazione di ciascuna fase la resistività del materiale, che è considerevolmente differente nei due stati.

Attualmente, leghe di elementi del VI gruppo della tavola periodica, quali Te o Se, anche chiamati calcogenuri o materiali calcogenici, possono essere utilizzati vantaggiosamente in celle di memoria a cambiamento di fase. Il calcogenuro che attualmente è più promettente è formato da una lega di Ge, Sb e Te

$(Ge_2Sb_2Te_5)$ , che è attualmente ampiamente utilizzata per immagazzinare informazioni in dischi sovrascrivibili.

Nei calcogenuri, la resistività varia di due o più ordini di grandezza quando il materiale passa dalla fase amorfa (più resistiva) a quella policristallina (più conduttiva) e viceversa, come mostrato in figura 1. Inoltre, nella fase amorfa, la resistività dipende notevolmente anche dalla temperatura, con variazioni di un ordine di grandezza ogni 100°C, con un comportamento simile a quello dei materiale semiconduttori di tipo P.

5

10

Il cambiamento di fase óuq essere ottenuto aumentando localmente la temperatura, come mostrato in figura 2. Al di sotto di 150°C, entrambe le fasi sono stabili. Al di sopra di 200°C (indicata come Tx. 15 temperatura di inizio nucleazione), si ha una rapida nucleazione dei cristalliti e se il materiale viene mantenuto alla temperatura di cristallizzazione per un tempo sufficiente (tempo  $t_2$ ), esso cambia di fase e diviene cristallino. Per riportare il calcogenuro nello 20 stato amorfo, è necessario alzare la temperatura al di sopra della temperatura di fusione Tm (circa 600°C) e quindi raffreddarlo rapidamente (tempo  $t_1$ ).

di Dal punto vista elettrico, è possibile raggiungere entrambe le temperature critiche (di 25 cristallizzazione e di fusione) facendo fluire

corrente attraverso un elemento resistivo cristallino che riscalda il materiale calcogenico per effetto Joule.

La struttura di base di un elemento di memoria a 5 cambiamento di fase 1 operante secondo i principi sopra descritti è mostrata in figura 3 e comprende un primo 2 elettrodo (di tipo resistivo, formante un riscaldatore); un elemento programmabile 3 un L'elemento programmabile 3 è secondo elettrodo 5. 10 realizzato calcogenuro con un viene deposto е normalmente nello stato policristallino dopo il trattamento. Una parte dell'elemento programmabile 3 è in contatto diretto con il primo elettrodo 2 e forma la. porzione attiva interessata dal cambiamento di fase, 15 chiamata in seguito porzione a cambiamento di fase 4.

Nell'elemento a cambiamento di fase 1 di figura 3, considerazioni tecnologiche ed elettriche impongono che l'area di contatto fra il primo elettrodo e l'elemento programmabile abbia piccole dimensioni di modo che, a parità di densità di corrente, l'operazione di scrittura possa essere eseguita con l'energia termica locale richiesta con minore consumo di corrente.

20

Sono state presentate diverse proposte per ridurre l'area di contatto. Per esempio US-A-6,294,452 descrive un procedimento per formare un'area di contatto di

dimensioni sublitografiche, basato sull'attacco isotropo di uno strato di polisilicio. Le dimensioni sublitografiche risultanti dipendono dalla qualità dell'attacco.

5 US 2001/0002046 descrive un procedimento per formare un elettrodo di un dispositivo di commutazione a calcogenuri, in cui uno strato spaziatore depositato in una apertura litografica viene attaccato in modo anisotropo e definisce lateralmente un elettrodo. La larghezza risultante dell'elettrodo dipende dallo spessore di uno strato spaziatore.

La domanda di brevetto europeo 01128461.9, depositata il 5.12.2001, e intitolata "Regione contatto di area ridotta, cella di memoria cambiamento di fase ad elevata efficienza e relativo 15 metodo di fabbricazione" descrive la formazione di un'area di contatto come intersezione di due porzioni sottili che si estendono trasversalmente una rispetto all'altra e ciascuna di dimensioni sublitografiche. Per formare le porzione sottili, si utilizza la deposizione 20 di strati.

In tutte le soluzioni precedenti indicate, qualunque variazione della larghezza L dell'elettrodo (figura 3), dovuta ad esempio a tolleranze di processo, influenza, in modo lineare, l'area di contatto della

25

regione attiva 4. Perciò, la larghezza L può avere tolleranze che non sono accettabili per quanto riguarda ripetibilità ed uniformità delle caratteristiche della cella.

5 Scopo dell'invenzione è quindi fornire una regione di contatto avente un'area meno dipendente dalle variazioni di processo.

Secondo la presente invenzione vengono realizzati un dispositivo elettronico a semiconduttore ed un procedimento per la fabbricazione di un dispositivo elettronico a semiconduttore, come definiti nelle rivendicazioni 1 e, rispettivamente, 9.

10

15

20

Secondo un primo aspetto dell'invenzione, l'area di contatto è formata lateralmente alla regione attiva ed ha una altezza e una larghezza. Vantaggiosamente, la larghezza dell'area di contatto è determinata dallo strato depositato, spessore di uno che tecnologicamente controllato e può essere progettato in essere sublitografico. Inoltre, secondo modo da altro aspetto dell'invenzione, la larghezza dell'area determinata dalla larghezza contatto è spaziatore che può anch'esso essere progettato dimensioni sublitografiche e può essere controllato dimensionamento con buona accuratezza.

25 Per la comprensione della presente invenzione ne

viene ora descritta una forma di realizzazione preferita, a puro titolo di esempio non limitativo, con riferimento ai disegni allegati, nei quali:

- la figura 1 mostra la caratteristica corrente tensione a basso campo di un materiale a cambiamento di fase;

- la figura 2 riporta il grafico temperatura-tempo di un materiale a cambiamento di fase;

- la figure 3 mostra la struttura di base di un 10 elemento di memoria PCM;

- la figura 4 mostra una sezione trasversale attraverso una struttura di contatto secondo l'invenzione;

- la figura 5 è una vista prospettica di una 15 porzione della struttura di contatto di figura 4 mostrante la variabilità dell'area di contatto a causa di tolleranze tecnologiche;

- la figura 6 è una sezione trasversale di un elemento di memoria PCM in una fase di fabbricazione 20 iniziale;

- le figure 7-11 sono sezioni trasversali di un dettaglio ingrandito di figura 6, in fasi di fabbricazione successive;

- la figura 12 è una vista prospettica della 25 struttura di figura 11; e

- le figure 13-16 sono sezioni trasversali dell'elemento di memoria PCM, in fasi di fabbricazione successive, prese in un piano perpendicolare a quello delle figure 7-11.

- 5 La figura 4 illustra la struttura di base di una di contatto secondo l'invenzione. In dettaglio, un dispositivo elettronico 90 ha un corpo 91 (ad esempio un substrato) di materiale monocristallino definente una superficie superiore 92 e una superficie 10 inferiore 93 ed alloggiante componenti elettronici 94, rappresentati schematicamente. Uno strato dielettrico 95 si estende al di sopra del corpo 91 e alloggia la struttura di contatto, indicata con 98. La struttura di contatto 98 è formata da un primo elettrodo 100 e da una regione attiva 103 di materiale calcogenico. 15 primo elettrodo 100, collegato ai componenti elettronici 94 come mostrato schematicamente per uno di essi, ha una porzione orizzontale 102 adiacente ed in contatto con la regione attiva 103. Un secondo o elettrodo 104 è formato sulla regione attiva 103 ed è 20 in collegamento elettrico con questa.

Come mostrato più chiaramente nella vista prospettica di figura 5, la porzione orizzontale 102 ha una forma allungata estendentesi lungo una direzione. longitudinale X parallela alle superfici superiore ed

25

inferiore 92, 93 del corpo 91. La porzione orizzontale 102 è delimitata longitudinalmente da una faccia di estremità 110. La faccia di estremità 110 si estende in un piano verticale che è idealmente perpendicolare alla direzione longitudinale X e quindi alle superfici superiore ed inferiore 92, 94, e definisce un'area di contatto laterale con la regione attiva 103. La faccia di estremità 110 è qui rettangolare ed ha una altezza S (estendentesi parallelamente alla direzione Z) e una larghezza W (estendentesi parallelamente alla direzione Y). La porzione della regione attiva 103 adiacente alla faccia di estremità 110 subisce un cambiamento di fase e quindi corrisponde alla regione attiva 4 di figura 3.

10

25

A causa della disposizione verticale della faccia di estremità 110 e quindi dell'area di contatto, l'altezza S è uguale allo spessore della porzione orizzontale 102 del primo elettrodo 100, e quindi può essere progettata in modo da essere sublitografica, cioè minore della dimensione minima ottenibile tramite litografia ottica UV.

In pratica, la struttura di contatto 98 secondo le figure 4, 5 è formata da una formazione allungata (porzione orizzontale 102 del primo elettrodo 100) avente un'estensione longitudinale parallela alla superficie superiore 92 del corpo 91 ed una faccia di

estremità 110 estendentesi in un piano verticale ed in contatto con la regione attiva 103, di modo che le dimensioni dell'area di contatto (definita dalla faccia di estremità 110) sono determinate dallo spessore S della formazione allungata e dalla sua larghezza W.

della porzione orizzontale L'altezza S quindi dell'area di contatto è più controllabile della larghezza L dell'elettrodo delle strutture di contatto precedenti (figura 3), di modo che le celle PCM aventi la struttura di contatto di figura 4 hanno dimensioni più uniformi delle celle della tecnica nota. La tolleranza di spessore di uno strato conduttivo formante la porzione orizzontale 102 consente, a parità dimensioni complessive, una migliore confidenza costruttiva rispetto ad elettrodi la cui area di contatto dipende dalla larghezza L.

10

15

L'altezza S dipende anche dalla qualità dell'operazione utilizzata per definire la faccia di estremità 110, in particolare dalla operazione 20 attacco utilizzata a tale scopo. La figura 5 mostra la possibile variazione dell'area di contatto nel caso che l'attacco non garantisca l'esatta verticalità della di estremità 110, di modo che la porzione orizzontale 102 ha una faccia di estremità inclinata, 25 indicata con 110', formante un angolo  $\alpha$  con la faccia

di estremità ideale 110 (che, come detto, è perpendicolare alla superficie superiore 92). In questo caso, l'altezza S' della faccia di estremità inclinata 110' è maggiore dell'altezza S di una quantità dipendente dall'angolo  $\alpha$ , dato che

$S' = S/\cos\alpha$ .

20

25

Nel caso peggiore, con le tecnologie attuali,  $\alpha \le 5^{\circ}$ , cosicché  $\cos\alpha \cong 1$  [ $\cos(5^{\circ})=0.99619$ ]. Dato che qualunque variazione dell'altezza S ha lo stesso impatto sull'area di contatto, la variazione dell'area di contatto dovuta a tolleranze di processo che influenzano l'altezza S è minore del 2%.

Inoltre, anche la larghezza W può essere sublitografica, utilizzando la tecnica dei 15 distanziatori, come descritto in sequito, con riferimento alle figure 7-12. Questa tecnica ha una tolleranza del ±10%.

Il processo per la fabbricazione della struttura di contatto di figura 4 verrà ora descritto con riferimento alle figure 6-16.

Inizialmente, figura 6, una fetta 10 comprendente un substrato 11 di tipo P, avente una superficie superiore 16, è soggetto a fasi standard di front end. In particolare, all'interno del substrato 11 vengono formate regioni di isolamento 12 che delimitano aree

attive; quindi, in successione, sono impiantate regioni di basse 13 di tipo N, regioni di contatto di base 14 di tipo N<sup>+</sup> e regioni di emettitore 15 di tipo P<sup>+</sup>. Le regioni di base 13, le regioni di contatto di base 14 e le regioni di emettitore 15 formano diodi o transistori bipolari che definiscono elementi di selezione per le celle di memoria.

5

Successivamente, un primo strato dielettrico viene depositato planarizzato; е aperture vengono 10 formate nel primo strato dielettrico 18 al di sopra delle regioni di contatto di base 14 e delle regioni di emettitore 15, е le aperture vengono riempite con tungsteno per formare contatti di emettitore 19a contatti di base 19b. Quindi, è depositato un secondo strato dielettrico 20 -per esempio, un vetro al silicio 15 non drogato (USG)-, e aperture 21, ad esempio di forma cilindrica, sono formate nel secondo strato dielettrico 20 al di sopra del contatto di emettitore 19a. Quindi, viene formata una regione a tazza 22, ad esempio 20 mediante deposito di uno strato di elettrodo, esempio di TiSiN, TiAlN or TiSiC, che riveste in modo conforme le pareti e il fondo delle aperture 21; quindi viene depositato un materiale dielettrico che riempie aperture 21 е successivamente il materiale 25 dielettrico e strato di elettrodo vengono rimossi

all'esterno delle aperture 21, usando tecniche di planarizzazione convenzionali, quali il CMP (Chemical Mechanical Polishing). La regione a tazza 22 quindi ha una parete verticale 22a che si estende lungo la superficie laterale cilindrica delle aperture 21.

5

10

15

20

25

Quindi, viene depositato uno strato conduttivo 27 (ad esempio di TaSiN, TiSiN, TiN, TiAlN, ecc.) avente uno spessore di 5-50 nm, corrispondente all'altezza desiderata S dell'area di contatto 110, ottenendo quindi la struttura di figura 6. Come visibile, lo strato conduttivo 27 si estende parallelamente alla superficie superiore 16 del substrato 11.

A questo punto, viene esposta una maschera e lo strato conduttivo 27 viene attaccato selettivamente allo scopo di formare strisce parallele nella direzione Y.

La larghezza di queste strisce deve essere sufficiente ad assicurare che, da un lato, l'anello conduttivo formato tocchino dalla verticale 28a e, dall'altro, siano tagliate dall'attacco trench descritto in figura 14.

Quindi, figura 7, viene depositato uno strato di delimitazione 29 di materiale isolante, ad esempio ossido. Lo strato di delimitazione 29 ha uno spessore di, ad esempio, 20-200 nm. Quindi, utilizzando una

maschera, una parte dello strato di delimitazione 29 viene rimosso tramite attacco dry per formare un gradino che ha un lato verticale 29a che si estende verticalmente di sopra del materiale dielettrico 23, e incrocia la parete verticale 22a della regione a tazza 22 (in un punto disposto davanti o dietro al piano del disegno, e quindi non visibile in figura 7).

5

10

In seguito, uno strato sacrificale 28, ad esempio nitruro con uno spessore di 5-50 nm, viene depositato in modo conforme. In particolare, lo strato sacrificale 28 forma una parete verticale 28a che si estende lungo il lato verticale 29a dello strato di delimitazione 29. Quindi si ottiene la struttura di figura 7.

In seguito (figura 8), lo strato sacrificale 28

subisce un attacco anisotropo che ha come conseguenza

la rimozione delle porzioni orizzontali dello strato

sacrificale 28 e di parte della parete verticale 28a.

Scegliendo appropriatamente lo spessore dello strato di

delimitazione 29 e lo spessore dello strato sacrificale

28 nonché il tempo e il tipo di attacco, è possibile

ottenere la larghezza sublitografica W desiderata per

la parte inferiore della parete verticale rimanente

28a.

Quindi, figura 9, la porzione rimanente dello 25 strato di delimitazione 29 viene rimossa e, figura 10, utilizzando la parete verticale 28a come maschera hard, lo strato conduttivo 27 viene definito. In seguito, figura 11, la parete verticale 28a viene rimossa.

Ora, come mostrato in prospettiva in figura 12, la

5 porzione rimanente dello strato conduttivo 27 (porzione

a striscia 27a) ha un'altezza S e una larghezza W.

Successivamente, figura 13, uno strato isolante 30 (ad esempio ossido di silicio) ed uno strato di adesione 31 (ad esempio Si, Ti, Ta, ecc.) sono depositati in sequenza.

10

Quindi, figure 14, viene aperto uno scavo 32 di dimensioni litografiche. Lo scavo 32 è una apertura avente una lunghezza predeterminata nella direzione perpendicolare al foglio del disegno, taglia 15 porzione a striscia 27a e si estende all'interno del secondo strato dielettrico 20 in modo da delimitare longitudinalmente la porzione а striscia 27a. pratica, lo scavo 32 determina la lunghezza L1 della porzione a striscia 27a.

In seguito, figura 15, uno strato calcogenico 33, ad esempio di Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> avente uno spessore di 20-200 nm, viene depositato in modo conforme e riempie lo scavo 32 con una porzione di area ridotta 33b, la cui forma e le cui dimensioni sono determinati dallo scavo 32.

25 Successivamente, uno strato di barriera 34, ad

esempio di Ti/TiN, e uno strato metallico 35, esempio di AlCu, sono depositati in sequenza al di sopra dello strato calcogenico 33; la pila formata dallo strato metallico 35, dallo strato barriera 34 e dallo strato calcogenico 33 viene definita utilizzando 5 una stessa maschera, formando in tal modo una linea di bit 41 includente una regione calcogenica 33a e regioni metalliche 34a, 35a. Infine, viene depositato un terzostrato dielettrico 42, che viene aperto al di sopra dei 10 contatti di base 19b. Le aperture così formate vengono riempite con tungsteno per formare contatti superiori 43 allo scopo di prolungare verso l'alto i contatti di base 19b. Quindi vengono eseguite fasi standard per formare linee di connessione in contatto con i contatti 15 superiori 43 e con le linee di bit 41, vengono formate piazzole di contatto e viene depositato uno strato di passivazione 45, definente una superficie principale 46 del dispositivo. Quindi, si ottiene la struttura finale di figura 16.

20 la In pratica, porzione а striscia 27a. (corrispondente alla porzione orizzontale 102 del primo elettrodo 100 di figura 4) ha una estensione longitudinale parallela alla superficie superiore 16 del substrato 11 e forma, con la porzione inferiore 25 della porzione di area ridotta 33b, di

contatto la cui altezza è definita dallo spessore dello strato conduttivo 27 e la cui larghezza è definita dallo spessore dello strato sacrificale 28. La qualità dell'attacco dello scavo 32 determina l'orientamento dell'area di contatto rispetto alla superficie superiore 16.

5

I vantaggi della presente invenzione sono chiari da quanto sopra. In particolare, si sottolinea il fatto che la struttura di presente contatto ha una 10 ripetibilità tecnologica molto buona, una minore dipendenza dalle variazioni di processo rispetto alle soluzioni della tecnica nota, pur mantenendo un'area di contatto molto piccola, avente dimensioni sublitografiche in entrambe le direzioni.

- Risulta infine chiaro che alla struttura di contatto e al procedimento qui descritti ed illustrati possono essere apportate numerose modifiche e varianti, tutte rientranti nell'ambito del concetto inventivo, come definito nelle rivendicazioni allegate.

- 20 In particolare, si sottolinea che la direzione porzione orizzontale 102 е dello strato conduttivo 27 è definita con riferimento alla superficie superiore 92, 16 del substrato, intendendo questo termine un piano corrispondente 25 superficie superiore originale della fetta. In pratica,

la porzione orizzontale 102 e lo strato conduttivo 27 sono perpendicolari alla direzione di crescita del substrato, dovuta alla deposizione dei vari strati superficiali. Se, a causa delle fasi di deposizione, crescita termica, attacco e impianto eseguite sulla fetta, la superficie superiore 16 del dispositivo finito non è più planare, si può fare riferimento alla superficie inferiore 93 del substrato o alla superficie principale del dispositivo 46.

Inoltre una forma di realizzazione alternativa della presente invenzione prevede che lo strato conduttivo 27 sia in contatto diretto con il contatto di emettitore 19a, evitando in questo modo gli strati dielettrici 20 e 23 e la regione a tazza 22.

5

## RIVENDICAZIONI

1. Dispositivo a semiconduttore elettronico (90) comprendente:

un corpo (91; 11) di materiale semiconduttore 5 avente una superficie superiore (92,16);

uno strato dielettrico (95; 20, 42) estendentesi al di sopra di detto corpo;

una regione di contatto (98) in detto strato dielettrico, detta struttura di contatto comprendente 10 una prima regione conduttiva (102; 27a) ed una seconda regione conduttiva (103; 33a), detta seconda regione conduttiva essendo di materiale calcogenico ed essendo in contatto elettrico con detta prima regione conduttiva,

- caratterizzato dal fatto che detta prima regione conduttiva (102; 27a) ha una forma a striscia avente una direzione longitudinale delimitata da una faccia di estremità (110) estendentesi trasversalmente a detta superficie superiore (92; 16) e formante un'area di contatto con detta seconda regione conduttiva (103; 33a).

- 2. Dispositivo secondo la rivendicazione 1, in cui detta prima regione conduttiva (102; 27a) si estende in una prima direzione (X) parallela a detta superficie superiore (92; 16).

- 3. Dispositivo secondo la rivendicazione 1 o 2, in cui detta faccia di estremità (110) è perpendicolare a detta superficie superiore (92; 16) entro tolleranze di processo.

- 5 4. Dispositivo secondo una qualsiasi delle rivendicazioni 1-3, in cui detta faccia di estremità (110) ha una forma complessivamente rettangolare avente una altezza (S) ed una larghezza (W).

- 5. Dispositivo secondo la rivendicazione 4, in cui 10 detta altezza (S) è compresa fra 5 e 50 nm e detta larghezza (W) è compresa fra 5 e 50 nm.

- 6. Dispositivo secondo una qualsiasi delle rivendicazioni 1-4, formante un dispositivo PCM includente una cella di memoria comprendente un 15 elemento di selezione (13-15)ed elemento un di immagazzinamento, detto elemento di immagazzinamento essendo formato da un elemento riscaldatore (22a, 27a) includente detta prima regione conduttiva (27a) ed una regione di immagazzinamento (33a) comprendente detta 20 seconda regione conduttiva.

- 7. Dispositivo secondo la rivendicazione 6, in cui detto elemento di selezione (13-15) è formato in detto corpo (11), un elettrodo inferiore (19a) si estende in detto strato dielettrico (20, 42) fra detto elemento di selezione e detta prima regione conduttiva (27a) ed un

25

elettrodo superiore (35a) si estende in detto strato dielettrico su detta seconda regione conduttiva (33a) e forma una linea di bit.

- 8. Dispositivo secondo la rivendicazione 7, in cui detta seconda regione conduttiva (33a) ha una porzione di area ridotta (33b) in contatto con detta prima regione conduttiva (27a) ed una porzione superiore allargata estendentesi al di sopra di detta porzione di area ridotta ed in contatto con detto elettrodo superiore (35a).

- 9. Procedimento per la fabbricazione di un dispositivo a semiconduttore elettronico (90), comprendente le fasi di:

fornire un corpo (91; 11) di materiale

15 semiconduttore avente una superficie superiore (92;

16);

formare uno strato dielettrico (95; 20, 42) estendentesi al di sopra di detto corpo; e

formare una struttura di contatto (98) in detto strato dielettrico, detta fase di formare una struttura di contatto comprendendo formare una prima regione conduttiva (102; 27a) e formare una seconda regione conduttiva (103; 33a) di materiale calcogenico in contatto elettrico con detta prima regione conduttiva;

25 caratterizzato dal fatto che detta fase di formare

detta prima regione conduttiva comprende formare una regione a striscia (102; 27a) avente una direzione longitudinale delimitata da una faccia di estremità (110) estendentesi trasversalmente a detta superficie superiore (92; 16);

5

10

15

25

- fase di detta formare una seconda regione conduttiva comprende formare detta seconda regione conduttiva (103; 33a) in contatto con detta prima regione conduttiva in corrispondenza di detta faccia di estremità.

- 10. Procedimento secondo la rivendicazione 9, detta faccia di estremità (110) ha una forma complessivamente rettangolare avente una altezza (S) compresa fra 5 e 50 nm ed altezza (W) compresa fra 5 e 50 nm.

- 11. Procedimento secondo la rivendicazione 9 o 10, in cui detta fase di formare detta prima regione conduttiva (27a) comprende depositare un primo strato conduttivo (27) su una porzione inferiore (20) di detto 20 strato dielettrico (20, 42); formare uno strato di delimitazione (29) al di sopra di detto primo strato conduttivo, detto strato di delimitazione (29) avendo gradino con una superficie di parete laterale verticale (29a); formare una porzione sacrificale (28a): detta superficie di parete laterale verticale;

rimuovere detto primo strato di delimitazione (29); attaccare detto primo strato conduttivo (27a) utilizzando detta porzione sacrificale (31a) come maschera; e rimuovere detta porzione sacrificale.

- 12. Procedimento secondo la rivendicazione 11, in cui detta fase di formare una porzione sacrificale (28a) comprende depositare uno strato sacrificale su detta prima regione conduttiva e detto strato di delimitazione (29) e attaccare anisotropicamente detto strato sacrificale (28).

- 13. Procedimento secondo la rivendicazione 11 12, in cui dopo la rimozione di detta porzione sacrificale (28a), uno strato isolante (30) viene depositato su detta prima regione conduttiva (27a) e 15 detta porzione inferiore di detto strato dielettrico (20, 42); uno scavo (32) viene formato per rimuovere almeno una parte di detta porzione inferiore ed una porzione terminale di detta prima regione conduttiva, definendo in tal modo detta superficie di estremità 20 (110); e viene depositato un secondo strato conduttivo (33) di detto materiale calcogenico, riempiendo detto scavo (32) e contattando detta faccia di estremità (110).

- 14. Procedimento secondo la rivendicazione 13, 25 comprendente la fase di formare un dispositivo PCM

cella di memoria comprendente includente una selezione (13-15)elemento di ed un elemento di immagazzinamento (33b),detto elemento di formato immagazzinamento essendo da un elemento riscaldatore includente detta prima regione conduttiva ed una regione di immagazzinamento comprendente detta seconda regione conduttiva.

5

15. Procedimento secondo la rivendicazione 14, comprendente, dopo il deposito di detta seconda regione 10 conduttiva (33), depositare uno strato di elettrodo (35) e definire detto strato di elettrodo e detto secondo strato conduttivo, per formare una linea di bit (41).

## RIASSUNTO

Una struttura di contatto (98) per un dispositivo PCM è costituita da una formazione allungata (102) avente un'estensione longitudinale parallela alla superficie 5 superiore (92) del corpo (91)ed una faccia di estremità (110) estendentesi in un piano verticale. La faccia di estremità (110)è in contatto con una porzione inferiore di una regione attiva (103)10 materiale calcogenico di modo che le dimensioni dell'area di contatto definite dalla faccia di. estremità (110) sono determinate dallo spessore (S) della formazione allungata e dalla sua larghezza (W).

15

Fig. 4

Fig.3

Fig.4